오늘은 transmission gate (줄여서 TM이라고도 부름), 혹은 switch라고도 부르는 셀 레이아웃에 대해 포스팅해 본다.

개인적으로 아날로그 레이아웃 업무로 다른 엔지니어들이 작업한 레이아웃을 들여다 볼 때도 많은데, 이 때 가장 아쉬운 부분이 많은 셀이기도 하다.

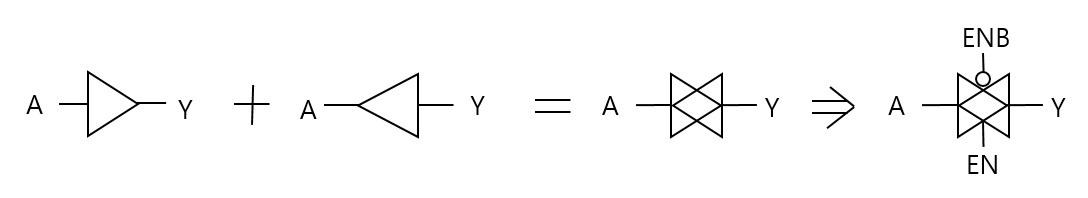

이 transmission gate의 symbol, schematic을 먼저 보자.

디지털 로직에서는 그냥 네모 박스로 symbol을 표현하기도 하지만, 흔히 아래와 같은 symbol로 많이 사용하는 편이다.

이 셀의 기능은 source와 drain이 병렬로 연결된 PMOS, NMOS를 동시에 ON, OFF 함으로써 ON 되었을 때만 data가 source 에서 drain으로, 또는 drain에서 source로 그대로 전달되도록 하는 셀이다.

NMOS,PMOS가 동시에 ON,OFF 되어야 하기 때문에 PMOS의 gate인 ENB와 NMOS의 gate인 EN은 항상 반대여야 한다.

일단 ON이 된 상태에서는 A,Y 양방향으로 신호가 전달 가능하기때문에 symbol을 자세히 뜯어보면 A to Y인 buffer와 Y to A인 buffer를 중첩시켜 놓은 모양임을 알 수 있다.

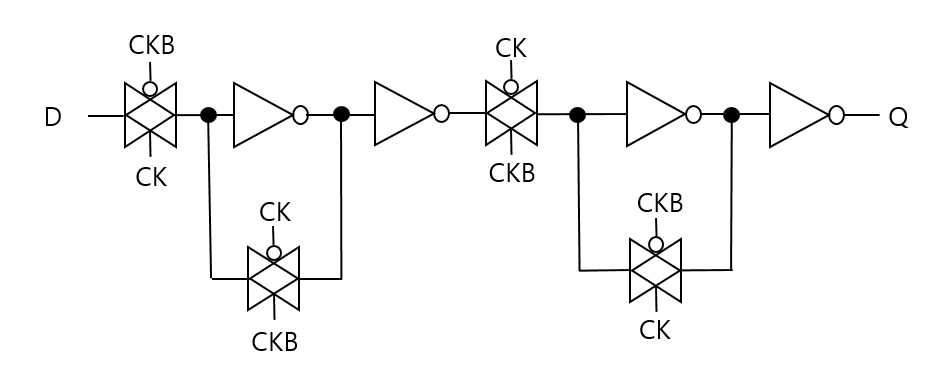

이 transmission gate를 가장 쉽게 볼 수 있는 회로가 clock 신호를 포함하는 sequencial 회로인 latch, flip-flop 회로를 예로 들 수 있겠다.

아래의 D-flip-flop 회로를 보면 네 개의 transmission gate를 포함하고 있는 것을 알 수 있다.

이 transmission gate 회로는 PMOS, NMOS가 병렬로 연결되어 있는 관계로 GND ~ VDD까지의 모든 신호를 잘 전달하는 특성을 가진다.

때문에 디지털 회로 뿐만 아니라 아날로그 회로에서도 아날로그 신호를 전달하기 위한 switch 용도로도 많이 이용하는 회로이다. 현업에서는 대체로 이 회로가 디지털 로직에 사용될 때는 transmission gate, 아날로그에서 사용할 때는 switch라고 부른다.

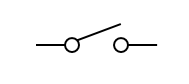

아래는 switch로 이용하기 위한 schematic 예가 되겠다.

많은 analog 회로에서 간략하게 아래와 같은 switch로 표시되어 있는 것들은 모두 위의 switch 회로라고 보면 된다.

그렇다면 이번에는 레이아웃 예를 들어보기로 한다.

아래 두 레이아웃을 살펴보자.

Layout A는 NMOS, PMOS의 gate 신호 연결을 위한 contact이 가운데에 자리잡고 있는 레이아웃이고, Layout B는 이들이 위, 아래로 위치하고 있는 레이아웃이다.

단순히 보면 Layout A의 크기가 더 크기 때문에 Layout B처럼 하라는 것인가? 하고 생각할 수도 있겠다.

이유는 다르지만 필자는 항상 Layout B 모양으로 그린다.

만약 레이아웃 사이즈 때문이라면 Layout A는 아래 레이아웃과 같이 가운데의 gate contact을 세로로 2개씩 사용하여 날씬하게 만들면 더 좋을 것이다.

그런데 필자가 Layout B로 권하는 이유는 따로 있다.

위에서 말한 바와 같이 이 회로는 analog 회로에서 switch로도 많이 사용되는 회로이다.

만약 내가 레이아웃 하는 transmission gate가 디지털 로직 안에서만 사용되는 것이라면 사실 Layout A처럼 하던 Layout B처럼 하던 상관은 없이 편한 대로 레이아웃 하면된다.

하지만 이 회로가 analog 신호 전달용으로 사용될 가능성이 있다면 이야기는 달라지는데, 위에서 예로 든 아날로그 회로에서의 switch 회로를 다시 한 번 가져와서 디지털, 아날로그 신호를 구분해 보도록 하자.

Analog 회로라면 위의 그림과 같이 NMOS, PMOS를 ON, OFF하는 신호는 디지털 신호이고, switch의 source, drain에 해당되는 부분은 analog 신호가 된다.

이 부분을 위의 레이아웃에 대응하는 부분으로 다시 보도록 하자.

자, 이렇게 레이아웃 상에서 analog, 디지털 영역을 나누어 보니 Layout A에서는 디지털 영역이 analog 영역 한가운데 자리잡게 되는 것을 알 수 있다. 그리고 이 디지털 신호가 clock 신호가 될 수도 있다는 것은 더욱 큰 문제가 될 수 있다.

이번에는 Layout A의 EN, ENB 신호를 연결하기 위해 아래와 같이 Metal2를 가로로 라우팅 해 준다고 가정해 보자.

이렇게 되면 누가 보더라도 두 개의 디지털 신호 라인이 A, Y의 아날로그 신호에 noise을 전달시킬 수 있다는 것을 알 수 있을 것이다.

Layout B에서 위와 같이 Metal2로 가로 라우팅을 하게 되더라도 A, Y와 겹쳐지는 부분이 없이 안전한 라우팅을 할 수 있다는 것을 알 수 있다.

사실 레이아웃을 처음 시작할 때 전체 회로가 완성된 상태에서 회로를 전달받는 경우는 드물고, 대부분은 일정을 줄이기 위해 일단 기본적인 로직 셀들부터 그리게 되는 경우가 많은 편이다.

이 때 transmission gate 회로가 디지털 로직에서만 사용되는지 아날로그 스위치로 사용될 지 모르고 레이아웃 해야 되는 상황이 너무 많기 때문에 습관적으로 Layout B와 같이 EN, ENB가 source, drain 신호를 방해하지 않도록 신경 써 주는 것이 중요하다.

특히 analog switch로 사용될 때는 저항을 줄여주기 위해 NMOS, PMOS를 multi 여러개로 사용하는 것도 흔한 일인데, 이 때 Layout A와 같이 레이아웃 한다면 아래 그림과 같이 A, Y 신호 연결도 더 복잡해지게 된다.

Analog 회로에서 위의 Layout B와 같이 레이아웃 했을 때 필자는 아래 그림의 빨간 점선으로 표시된 부분에서 EN, ENB와의 parasitic 성분이 생기는 것을 줄여주기 위해 이 부분을 없애고 M2로 연결하곤 한다.

이렇게 M2로 두껍게 라우팅 할 수 있으면 저항을 줄여 줄 수 있다.

정리하자면, 디지털 로직으로만 사용하는 transmission gate는 Layout A, Layout B 중 어느 형태로 레이아웃 하더라도 상관이 없다. 하지만 analog 로 사용될 경우에는 반드시 Layout B 형태로 레이아웃 하기로 한다.

레이아웃 엔지니어들의 경우 회로 중 analog, 디지털 영역을 구분하기 어려워 하는 사람들이 무척 많은데, NMOS, PMOS의 source, drain 양 쪽 모두 0,1로만 표현되는 inverter, nand, nor, flip-fop 등의 로직 게이트로 연결되어 있다면 이는 디지털 회로로 사용된 것이지만, 한쪽이라도 저항이나 capacitor 연결되어 있다면 analog 회로로 사용된 것이라 판단하면 좀 더 쉬울 것이다.

이렇게 매 번 판단하고 레이아웃 모양을 다르게 하는 것이 귀찮고 비효율적이므로 항상 Layout B 형태로 레이아웃 하도록 하는 것을 권하는 것으로 이번 포스팅 마무리를 하도록 하겠다.

'Logic 레이아웃' 카테고리의 다른 글

| 로직 회로의 파워 그라운드 레이아웃 (0) | 2025.02.16 |

|---|---|

| 그대로 따라 그리는 로직 레이아웃 - edge triggered D flip-flop (4) | 2025.01.10 |

| 그대로 따라 그리는 로직 레이아웃 - schmitt trigger buffer (2) | 2024.11.18 |

| 그대로 따라 그리는 로직 레이아웃 - buffer,nand,nor (0) | 2024.11.12 |

| 그대로 따라 그리는 로직 레이아웃- 레이아웃의 시작, 인버터 (7) | 2024.10.17 |