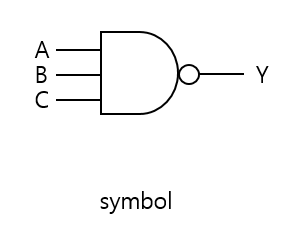

이번 포스팅에서는 인버터를 포함하여 아날로그 블럭 내 콘트롤 로직의 거의 90% 이상을 차지하는 buffer, nand, nor 레이아웃 예제를 보여주기로 한다.

로직 레이아웃 시 기본 사항은 이전의 미리 알아둘 내용 및 인버터 포스팅에서 다루었기 때문에 주로 패턴만 보여주는 데 중점을 줄 것이므로 눈으로 보고 익혀두면 도움이 될 것이다.

Buffer layout

버퍼 사이즈를 줄이기 위해서는 위의 레이아웃과 같이 active layer를 공유하는 것이 좋다.

하지만 위의 schematic2와 같은 회로로 되어 있다면 아래와 같이 인버터 각각의 active를 분리하기도 하는데, 이는 레이아웃 엔지니어의 선택의 문제이다.

필자의 경우는 처음 디바이스를 뿌리는 단계에서는 일단 아래와 같이 인버터를 분리하는 쪽을 선택하는 편인데, 레이아웃을 진행하다 보면 설계상의 이유로 약간의 로직이 추가되는 경우가 흔하게 있기 때문에 그 때 필요하게 될 지 모르는 공간을 확보해 놓기 위한 용도로 쓰기 위해서 그렇게 한다. (로직이 추가되어 공간이 부족하면 위와 같이 buffer의 active를 merge하여 필요한 공간을 확보함)

다만 레이아웃 상의 공간이 처음부터 너무 빡빡할 때는 위와 같이 active를 merge하는 것이 좋겠다.

아래는 권하지 않는 buffer 레이아웃의 예이다.

잘 보면 알겠지만 앞, 뒤 inverter의 연결을 M2로 연결했는데, M1으로 바로 연결할 수 있는 곳에서 굳이 M2를 사용하는 것을 권하지 않는다.

로직을 모아서 라우팅을 해 보면 알겠지만, 로직라우팅에서 가장 아쉬운 메탈이 M2 레이어이기 때문에 M2 대신 M1을 사용하여 라우팅이 가능한 곳을 최대한 M1으로 해결하는 습관을 들이는 것이 좋다.

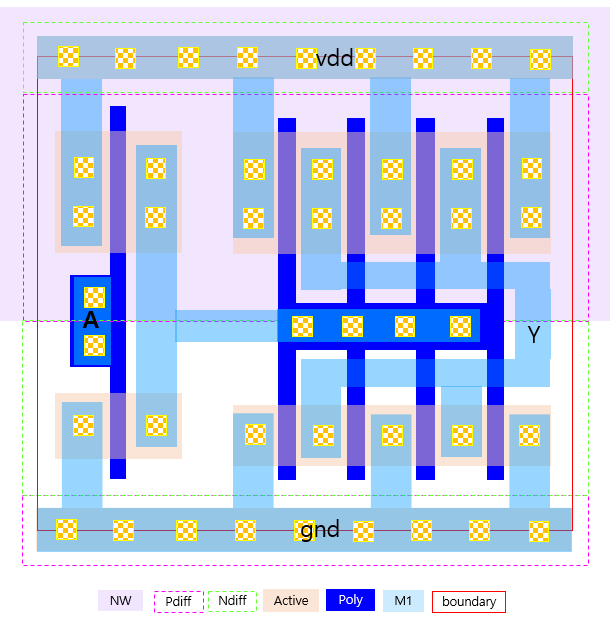

2 input NAND layout

NAND나 NOR 레이아웃을 할 때는 series로 연결되어 있는 MOS 사이의 source, drain contact은 지워버리는 것이 좋다.

그 부분의 contact은 외부와 연결되지 않기 때문에 필요도 없을 뿐더러 contact이 있게 되면 M1 라우팅에 제한을 받게 되고 불필요한 load cap 성분이 추가되므로 PDK 옵션에서 contact을 삭제하도록 한다.

하지만 multi 갯수가 2개 이상으로 되면 series 연결된 부분도 아래의 레이아웃처럼 contact이 필요해 진다.

M2 사용을 최대한 줄이기 위해서는 M1 라우팅을 아래위로 좀 돌려줄 필요가 있다.

2 input NOR layout

NOR 레이아웃은 NAND와 위아래만 뒤집으면 똑같은 모양이다.

실제로 바쁠때는 NAND layout의 복사해와서 위아래로 뒤집은 후 N, PMOS 만 옮겨 주기도 한다.

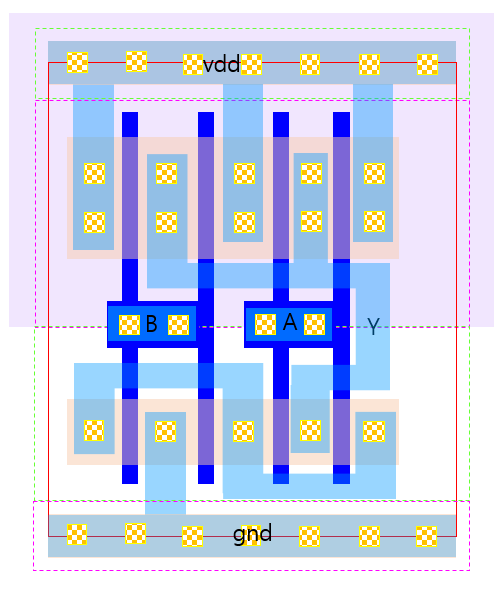

3 input NAND layout

3-input NAND, NOR에서 각 MOS의 finger가 2개 이상으로 되면 어쩔 수 없이 active를 분리해 줘야 한다.

finger 갯수에 따라 M2를 사용해야 하는 경우도 발생하니 회로 각각의 finger 갯수에 따라 선택하면 되겠다.

포스팅에서 보여 주는 것은 어디까지나 "예제" 임을 잊지 말자.

중요한 것은 주어진 공간 안에 레이아웃을 구겨넣을 수만 있으면 active를 분리하던, M2로 올리던 큰 상관이 없다.

다만 공간이 항상 부족해서 문제인거...ㅠㅠ

3 input NOR layout

3-input NOR 역시 3-input NAND와 위아래 flip된 모양의 라우팅이다.

뭐, 이 정도로 보고 나니 별거 없어보인다.

다만 현업에서는 각각의 아날로그 블럭마다, 회로 설계자마다 지금까지 예로 들어준 인버터, buffer, nand, nor를 제각각 따로 따로 만들어서 쓴다.

그래서 이런 로직들만 기본 수십개를 레이아웃 해야 하는 것이 문제.

때로는 똑같은 사이즈의 로직들인데 이름만 다른 경우도 많다.

레이아웃 효율화를 위해 로직을 공용으로 사용하고자 하는 시도는 항상 나오는 말이지만 이 또한 말처럼 쉽지만은 않은 일이라 인버터, buffer, nand, nor 정도는 뚝딱뚝딱 레이아웃 해서 쓰는 것이 오히려 마음 편하기도 한 듯......

어쩌다 신세한탄이 되어 버린 이번 포스팅은 이것으로 마무리!

'Logic 레이아웃' 카테고리의 다른 글

| 그대로 따라 그리는 로직 레이아웃 - edge triggered D flip-flop (4) | 2025.01.10 |

|---|---|

| 그대로 따라 그리는 로직 레이아웃 - transmission gate (또는 switch) (2) | 2024.11.24 |

| 그대로 따라 그리는 로직 레이아웃 - schmitt trigger buffer (2) | 2024.11.18 |

| 그대로 따라 그리는 로직 레이아웃- 레이아웃의 시작, 인버터 (7) | 2024.10.17 |

| 그대로 따라 그리는 로직 레이아웃 - 미리 알아두어야 할 내용들 (4) | 2024.10.03 |