앞선 포스팅에서 다뤘던 inverter, buffer, nand, nor 로직 레이아웃을 잘 익혔다면 단순 로직 셀들의 레이아웃은 이제 식은죽 먹기일 것이다.

이번 포스팅은 schmitt-trigger buffer 레이아웃의 주의사항을 살펴보도록 하겠다.

먼저 schmitt-trigger buffer 에 대해 최대한 간단히 설명해 보자면, 일반적인 CMOS buffer는 intput 신호가 GND 와 VDD 사이에서 올라가거나 내려갈 때 0.5VDD에서 switching이 일어나는 것에 비해, schmitt-trigger buffer는 input 신호가 GND에서 VDD로 올라 갈 때는 0.5VDD보다 높은 전압에서 switching이 일어나며, input 신호가 VDD에서 GND로 내려 갈 때는 0.5VDD보나 낮은 전압에서 swiching이 일어나도록 설계 된 buffer라고 할 수 있다.

이해를 돕기 위해 일반 CMOS buffer와 schmitt-trigger buffer의 in-out DC특성 곡선을 보기로 하자.

위의 schmitt-trigger buffer의 DC 특성을 보면 input 전압이 올라 갈 때와 내려 갈 때의 switching point가 다르다는 것을 알 수 있다. 이 그래프의 VT+와 VT- 신호의 차이를 hysteresis 전압이라고 부른다.

이런 특성을 갖는 buffer을 사용하는 이유는 input 신호에 noise가 있을 경우그 noise 성분이 그대로 output으로 전달되는 것을 막기 위해서이다.

이 또한 이해를 돕기 위해 noise 성분이 있는 AC 신호의 예를 들어 보겠다.

위의 그림은 0.5VDD 근처에서 noise가 있는 input 신호에 대한 CMOS buffer와 schmitt-trigger buffer의 output 파형을 보여준다.

먼저 CMOS buffer의 동작은 0.5VDD에서 switching이 발생하기 때문에 noise 성분이 그대로 output으로 반영되는 것을 알 수 있다.

하지만 schmitt-trigger의 경우에는, rising 신호에서 VT+에 도달하기 전까지는 switching이 일어나지 않는다. 때문에 VT+ 보다 낮은 전압의 noise는 반영되지 않고 신호가 VT+에 도달하였을 때 output 신호는 GND 에서 VDD로 switching이 된다.

일단 VDD로 switching이 되고 난 후에는 이번에는 input 신호가 VT-까지 내려와야만 GND로 switching이 일어나게 되므로 VDD ~ VT- 사이에서 발생하는 noise는 output 신호에 영향을 주지 않게 된다.

따라서 VT+와 VT- 의 차이인 hysteresis 전압은 곧 schmitt-trigger의 noise immunity를 나타낸다고도 할 수 있다.

이러한 schmitt-trigger buffer를 나타내는 symbol은 아래와 같다.

Rising과 falling switching 전압이 다르다는 점을 나타내는 특성곡선을 buffer 안에 표시하는 것이 일반적이다.

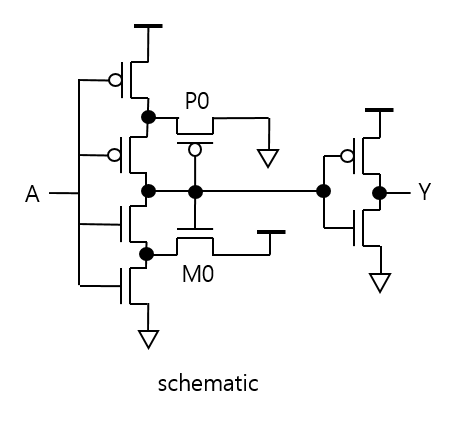

Schmitt-trigger를 CMOS로 구현하는 회로는 여러가지가 있는데, 아래의 회로가 가장 일반적으로 사용되고 있는 회로이다.

P0,M0로 표시된 MOS가 hysteresis 전압을 결정하는 역할을 하게 된다.

Truth table은 물론 일반 CMOS와 같다.

위의 회로의 모든 MOS가 동일한 width, length를 가지고 있다고 가정한 레이아웃 예이다.

회로를 잘 살펴보면 P0는 PMOS이지만 source가 GND에, M0는 NMOS이지만 source가 VDD로 연결되어 있다는 점을 알 수 있을 것이다. 이 두 MOS가 위치하고 있는 영역과 반대쪽에 있는 VDD, GND 신호를 각각 끌고 와서 연결해 주어야 하기 때문에 보통은 M2를 사용할 수 밖에 없다.

자, schmitt-trigger buffer 하나를 위해 이렇게 별도의 포스팅을 하는 이유는 이렇게 반대쪽 GND, VDD에 연결되어야 하는 P0, M0 때문이다.위의 레이아웃 예를 자세히 보면 M0, P0 MOS와 인접하고 있는 output inverter에도 VDD, GND가 연결되어 있는 것을 알 수 있는데, 아래의 그림에 빨간 점선으로 표시하여 보았다.

이렇게 VDD와 GND에 각각 연결되어 있는 두 active가 가까이 붙어있게 되면 ESD에 아주 취약한 레이아웃이 되어버린다. Power-ground 사이에 ESD 전압이 유입 시 위의 빨간 점선으로 표시 된 부분에서 damage가 발생할 수 있다.

일부 파운드리 업체에서는 이런 부분을 DRC로 체크하기도 하는데, 문제는 어떤 업체는 ESD DRC rule을 사전에 배포하지 않는 곳도 있다는 것이다.

그래서 tape-out 용 DRC,LVS 검증을 다 끝내고서 GDS file을 파운드리 업체에 전달 한 후에 저런 부분이 발견되는 경우도 있다. 그렇게 된다면 그야말로 맨붕...... (필자가 직접 겪었던 상황임 ㅠㅠ)

그래도 mask 제작 이전에 저런 부분을 발견할 수 있다면 다행이다.

만약 저상태로 chip 제작이 완료된 후에 ESD 이슈가 발생한다면 그 때는 chip도 죽고 나도 죽도록 털리는 상황이 될 수도 있다.

그렇다면 해결책은?

아래 그림에서 파란색 화살표로 표시한 부분처럼 공간을 띄워 주면 간단히 해결된다.

보통 이 부분을 체크하게 되어 있는 design rule에서는 특정한 값 이상 띄워주면 되지만 별도로 체크하는 rule이 없는 경우도 있기 때문에 적당히 알아서 띄워줘야 한다.

아니면 output단 쪽의 inverter를 좌우로 뒤집어서 GND, VDD로 바로 연결된 active가 마주보고 있지 않게만 해도 된다.

하지만 이런 경우에는 routing이 귀찮아지기 때문에 필자의 경우에는 파란 화살표 있는 영역에 inverter 하나 들어갈 수 있을 정도의 공간을 확보해 주는 편이다.

물론 schmitt-trigger 회로에 따라 레이아웃 모양이 달라질 수 있겠지만, 위에서 말한 바와 같이 VDD, GND에 각각 연결된 active가 너무 가까이 있지 않도록 레이아웃해야 한다는 점을 명심하는 것이 이번 포스팅의 목적이 되겠다.

'Logic 레이아웃' 카테고리의 다른 글

| 그대로 따라 그리는 로직 레이아웃 - edge triggered D flip-flop (4) | 2025.01.10 |

|---|---|

| 그대로 따라 그리는 로직 레이아웃 - transmission gate (또는 switch) (2) | 2024.11.24 |

| 그대로 따라 그리는 로직 레이아웃 - buffer,nand,nor (0) | 2024.11.12 |

| 그대로 따라 그리는 로직 레이아웃- 레이아웃의 시작, 인버터 (7) | 2024.10.17 |

| 그대로 따라 그리는 로직 레이아웃 - 미리 알아두어야 할 내용들 (4) | 2024.10.03 |