아날로그 설계자들에게 "아날로그 레이아웃 할 때 가장 중요한 것이 뭔가요?" 라고 묻는다면 열이면 열명 모두 "당연히 레이아웃 matching이죠!" 라고 대답할 정도로 matching은 아날로그 레이아웃의 핵심 개념이다.

그래서 경력직 면접의 단골 질문으로 나오기도 하니 무엇보다 matching에 관한 내용을 먼저 다뤄야 할 것 같다.

그 전에 먼저, 아날로그 설계에서 레이아웃이 왜 중요한지 먼저 설명하고자 한다.

간단히 디지털 회로와 비교해 보면, 디지털 동작은 알다시피 1 과 0의 동작이다. 그래서 신호는 power(VDD), ground(VSS)둘 중의 하나로 stage가 정해 질 뿐이므로 클럭 주파수가 GHz 단위의 고속 동작이 아닐 경우에는 사실 레이아웃의 parasitic R, C 성분에 의해 회로적인 특성이 스펙을 벗어나는 경우는 별로 없다고 볼 수 있다.

하지만 아날로그 회로는 디지털 회로와 달리 1과 0 사이의 무수히 많은 값을 의미있는 신호로 다루기 때문에 레이아웃의 영향이 엄청나다.

쉽게 예를 들어 보자. 10비트 DAC(Digital to Analog Converter)를 예로 들어 보면, 이 회로는 10비트, 즉 0000000000부터 1111111111 까지의 디지털 신호를 아날로그 신호로 변경하는 회로이므로, VSS에서 VDD까지의 output 전압레벨을 1024개의 레벨로 나누어 출력해야 한다는 말이 된다.(디지털에서는 단 두 개였다)

그러니 만약 그 전압레벨을 (쉽게 이해 할 수 있는 예로) 저항으로 나누게 된다면 각각의 저항 비율이 엄청나게 중요하게 되는 것이다. 그런데 이 저항들을 라우팅 할 때 메탈 길이에서 차이가 발생하여 저항 비율에 영향을 주게 되면 DAC 특성이 나빠지게 되는 것 쯤은 쉽게 생각할 수 있다.

결론은 아날로그 회로에서는 parasitic R,C 값이 어마어마하게 중요하다는 뜻.

예로 든 것과 같이 ADC건 DAC건 간에 10bit 이상인 회로를 맡았다면 라우팅 한 땀 한 땀, 디바이스 배치 하나 하나 이론대로 배치하고 라우팅 해야 레이아웃 때문에 과제가 실패했다는 소리를 면할 수 있을 것이다.

Chip 하나가 성공하기 위해서 수백 가지의 항목들을 통과하더라도 단 하나의 에러만 발생하면 그것은 실패한 chip이 되고만다.

회로 설계자의 경우, post-simulation을 통하여 특성 확인을 마치면 사실상 그들이 할 수 있는 것을 다 한 것이지만 불행히도 chip이 만들어져 나오기까지는 simulation으로 검증 할 수 없는 항목들도 다수 존재한다.

그래서 특히 아날로그 레이아웃 엔지니어는 이렇게 검증 불가능한 항목들도 대비할 수 있는 패턴으로 레이아웃을 해야 하는데, 사실 이 작업은 해도 해도 끝이 없다.

그래도 꼼꼼히 확인하고 심각한 문제가 발견되면 tape-out 일정을 미뤄서라도 수정 후 tape-out을 하는 게 유리하다.

Chip 한 번 만드는 비용은 생각보다 비싸다. Planar 공정으로 메탈 하나 고치는 것도 몇 백 만원부터이고, 재수 없게 전체 레이어를 수정해야 하는 경우(우리는 이것을 full layer revision이라고 부른다) 최소 몇 천, 최신 FINFET 공정 full layer revision은 10억 이상일 정도이다. 즉, 한 번에 레이아웃을 말끔하게 잘 끝내는 것이 가장 중요하다는 점은 항상 명심해야겠다.

그래서 본론으로 들어가자면,

Matching 레이아웃이란?

Mismatch의 종류?

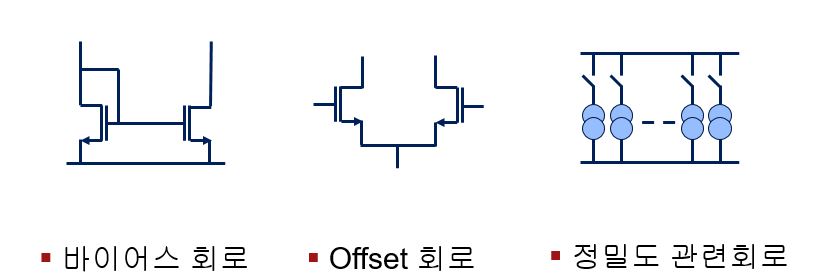

Mismatch 원인에 따라 크게 다음과 같이 세 가지로 나눈다.

- Systematic mismatch

- Random mismatch

- Gradients mismatch

Systematic mismatch

주로 회로설계자나, 레이아웃 설계자에 의해 발생되는 기본적인 mismatch.

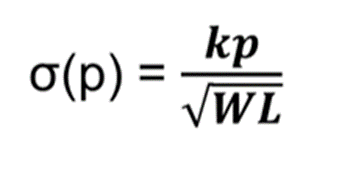

Random mismatch

Random mismatch는 WL의 제곱근에 반비례함을 알 수 있다.

즉, random mismatch를 2배 줄이려면 면적을 4배 늘려야 한다는 뜻으로, 정밀한 matching을 위해서는 큰 사이즈의 디바이스가 필요하다는 것을 알려주는 수식이다.

중요 아날로그 회로의 Tr은 minimum 값보다 훨씬 크다는 점은 이 random mismatch를 줄이기 위한 결과로 볼 수 있다.

Tr의 length가 작을수록 Tr 동작이 빨라지므로 speed와 같이 성능이 중요할 경우 matching 조건과 충돌할 수 있다.

<Random mismatch를 줄이는 법>

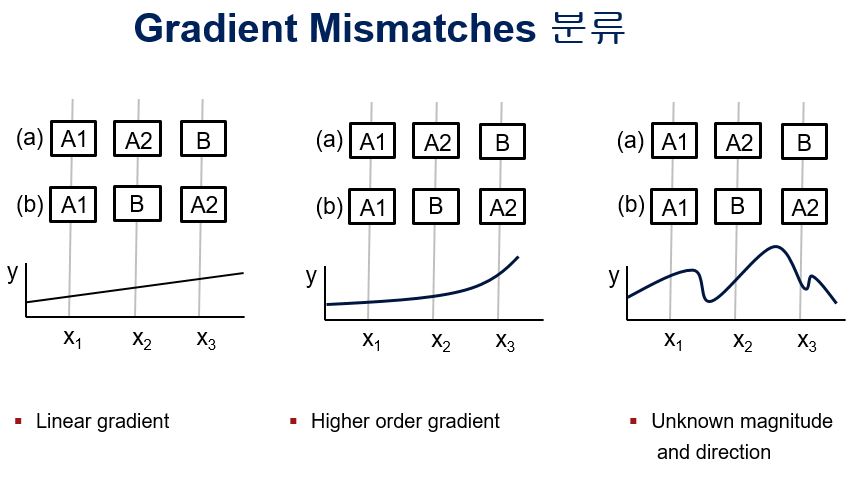

Gradients mismatch

Chip 표면 단 차, chip 위치에 따른 온도 변화 등 칩 전체에 걸친 1,2차 변동사항으로

<Gradients mismatch를 줄이는 법>

•Common-centroid

•Interdigitation

Matching technique 은 다음 포스팅에! -- Comming soon!

'IC레이아웃' 카테고리의 다른 글

| Planar CMOS process (0) | 2024.06.14 |

|---|---|

| Matching Technique - Common centroid & Interdigitation (2) | 2024.06.07 |

| 레이아웃을 위한 반도체 공정(process) 기본 개념 (0) | 2024.05.25 |

| [아날로그 레이아웃]Planar CMOS와 FINFET layout 차이점 (4) | 2024.05.06 |

| 블로그를 시작하며 (4) | 2024.04.15 |