아날로그 레이아웃에서 가장 중요한 점은 current mirror, differential pair 등의 중요 회로에서의 디바이스 간 매칭이라고 할 수 있다. 그러나 반도체 공정 진행 중에 발생하는 여러 변수들은 설계된 아날로그 회로의 정확도나 원하는 성능에 영향을 줄 수 있다.

각 디바이스 별 매칭 기술은 별도로 포스팅 하겠지만, 디바이스 공통으로 적용되기도 하면서 레이아웃 매칭에서 가장 중요하다고 할 수 있는 디바이스 배치 형태인 common centroid 와 interdigitation에 대해 별도로 설명해 보고자 한다.

특히 gradient effect에 의한 mismatch를 방지하기 위해서는 디바이스 배치가 거의 레이아웃의 생명이나 다름없고, 레이아웃 채용 관련 면접에서의 단골 질문이기도 하므로 레이아웃 엔지니어들이라면 잘 숙지한 후 업무에 적용하기를 권한다.

(실제 디바이스에서의 배치 예는 각 디바이스 매칭 기술 포스팅에서 다룰 예정이므로 참고 바람)

Common Centroid란?

말 그대로 공통의 중심을 갖도록 배치하는 것을 뜻하는데, 먼저 중심(Centroid)를 찾는 방법부터 알아보도록 하자.

- 기하학적 도형에 대칭되는 축이 있으면 중심은 그 축 위에 놓인다.

- 기하학적 도형에 두 개 이상의 대칭축이 있는 경우 중심은 대칭축들의 교차점에 있어야 한다.

위의 그림을 보면 아주 쉽게 이해할 수 있을 것이다. 좌/우, 상/하의 대칭되는 축이 바로 Centroid이다.

그렇다면 하나의 디바이스 말고 여러 개의 디바이스에 대하여 생각해 보자.

디바이스 배열의 중심은 그 배열을 이루는 디바이스들의 중심점으로부터 계산될 수 있다.

즉, 배열의 모든 디바이스들이 크기가 동일한 경우, 배열의 중심 위치(centroid)는 각 디바이스들의 중심의 평균이 된다. 이 때 centroid는 반드시 디바이스 영역 안에 있어야 할 필요는 없다. (디바이스 사이 빈 공간이 centroid여도 된다는 뜻)

적절하게 구성된 두 개 이상의 배열이 동일한 중심을 가지도록 배치할 수 있는데, 이런 배치를 common centroid라고 한다.

Interdigitation 이란?

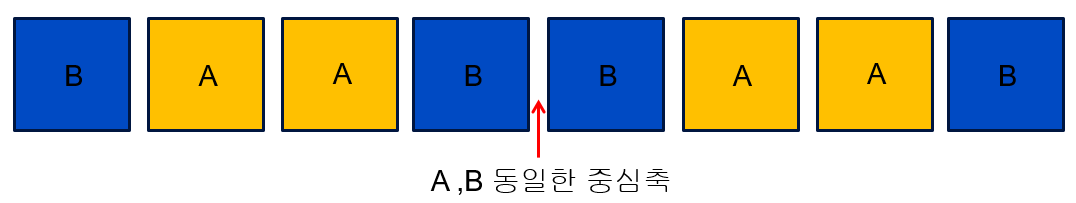

가장 간단한 종류의 common centroid 배열은 1차원으로 배열된 디바이스로 구성된다.

아래 그림과 같이 1차원 common-centroid 배열은 저항과 같은 얇고 길쭉하게 생긴 디바이스 배치에 이상적인데, 매치해야 하는 디바이스가 교차로 배열을 형성하기 때문에 이런 배치를 interdigitation이라고 부른다.

모든 intergitated 배열이 똑같이 만들어지는 것은 아니다.

이상적으로는 아래의 A,C 그림과 같이 배열은 매치해야 할 디바이스의 centroid를 기준으로 정확하게 정렬해야 하지만, B와 같이 약간의 중심 차이가 있도록 배열 할 수도 있다. 즉, A,C 는 interdigitation이면서 common centroid 배치이지만 B는 common centroid는 아닌 interdigitated 배치이다.

다시 한 번 정리하면,

Common centroid 배치 : 디바이스들이 동일한 중심점을 갖도록 배치하는 방법

Interdigitation technique : 디바이스를 교차로 배치하는 방법

Cross-coupled array

위에서 설명한 1차원적인 배치 방법은 X축의 linear mismatch 요소에 대해서만 효과가 있는 배치 방법이다.실제 mismatch 요인들의 방향성을 알 수는 없으므로, 중요 디바이스 배치 시에는 Y축에 대한 고려도 필요하다.

그래서 매치시켜야 하는 디바이스가 전체 4개 이상일 때에는 아래와 같이 cross-coupled array를 적용 해 주어야 한다.

Cross-coupled라는 말처럼 A, B 디바이스 두개씩이 교차된 모습으로 배치하는 형태이다.

8개의 디바이스를 배치할 때는 Y축을 기준으로 mirror 형태가 되는 점을 주의할 것.

위의 A와 같은 배치는 cross-coupled 배치의 가장 기본적인 형태로 cross-coupled pair 라고 부른다. 작은 크기의 다수의 디바이스를 배치 시 이 cross-coupled 배치가 가장 이상적인 배치라고 할 수 있다.

특히 디바이스 개수가 많아지면 cross-coupled 가 아닌 tiling이라는 용어를 사용한다.타일을 깔듯이 많은 수의 디바이스를 쭉 깔아서 배치한다는 뜻으로 물론 이 때도 조금 복잡해 보이는 규칙에 따라 배치하여야 좋은 매칭 특성을 얻을 수 있다.

자, 다음 설명으로 넘어가기 전에 common centroid 배치 시 고려해야 할 사항들을 정리해 보겠다.

1. 일치 : 매칭되어야 하는 디바이스의 중심은 대략 일치해야 한다. 이상적으로는 중심이 정확히 일치해야 한다.

2. 대칭 : 배치는 X축과 Y축 모두에 대해 대칭이어야 한다.

3. 분산 : 배치는 가능한 최고 수준의 분산을 보여야 한다. 즉, 각 디바이스들은 배치 영역 전반에 가능한 균일하게 분산되어 있어야 한다.

4. 사이즈 : 배치된 영역는 가능한 작아야 하며, 이상적으로는 거의 정사작형이어야 한다.

위에서 설명한 기본 개념을 바탕으로, 비선형 gradient mismatch 요소을 제거하기 위한 N차 common centroid 레이아웃 배치에 대해 알아보자.

위의 common-centroid와 inter-digitation 배치 기술은 특히 gradient mismatch 방지를 위해 꼭 필요하다.

그렇다면 gradient mismatch란 어떤 것들이 있을까? 우리말로 직역하면 "기울기" 인데, 대체 어떤 기울기란 말이지? 하는 의문이 들 것이다. 필자는 기울기보다는 "점진적 변화"라고 이해하는 것을 권한다.

사실 gradient mismatch는 가장 이해하기 쉬우면서도 예측이나 simulation이 불가능하기 때문에 어쩌면 가장 어려운 mismatch 요소가 될 수도 있을 것 같다.

몇 가지 예를 들어 보자.

<Gradient mismatch 요소의 예>

1. 웨이퍼 표면의 높낮이 변화 : 반도체 웨이퍼는 이상적으로 편평하지 않고 조금씩 높낮이가 다르다. 웨이퍼 마다 다를 수 있고 하나의 웨이퍼 표면에서도 위치에 따라 다를 수 있으며 이는 패턴의 크기나 oxide 두께에 영향을 준다.

2. 광원 : Photo 공정 시 UV 광원에서 mask, 웨이퍼로 이어지는 빛 또한 이상적으로 웨이퍼의 모든 곳에 90도 각도로 들어오는 것은 아니다. 보통은 웨이퍼 센터를 기준으로 가장자리로 갈수록 각도가 틀어지게 되어 있다.

3. 압력 : 만약 회로가 bump 아래쪽에 존재하게 된다면 다른 위치에 있는 회로에 비해 높은 압력으로 눌리게 된다. 이 압력도 디바이스 특성을 변화시키는 요인이 될 수 있다.

4. 온도 : 디바이스 근처에 많은 전류를 구동하는 회로가 있거나 clock driver 등이 존재한다면 가까이 위치한 디바이스의 특성(특히 저항 특성)이 바뀌게 된다.

위와 같이 예로 든 gradient mismatch 요소들은 하나같이 패턴이나 디바이스 특성에 영향을 미치지만 parameter로 뽑을 수 없는 것들이다. 동시에 디바이스가 놓인 위치에 따라 받는 영향이 점진적으로 변화한다는 특징이 있다. 바로 이러한 요소들을 gradient mismatch 요인이라고 부르는 것들이다.

그렇다면 이제 gradient 영향과 디바이스 배치와의 상관관계를 도식화하여 보기로 하자.

위의 그림과 같이 분홍 화살표가 있는 곳으로부터 점진적으로 linear gradient 영향을 받는 두 디바이스가 있다고 가정하자.

당연히 파란 디바이스가 노란것에 비해 영향을 많이 받을 것이다.

하지만 이렇게 각각의 디바이스를 두 개로 나눈 후 common centroid로 배치를 하게 되면 노랑, 파랑 디바이스들이 받는 평균적인 영향은 거의 같아 질 수 있다.

하지만 실제 gradient mismatch 요소가 위와 같이 linear 하지는 않을 것이다.

사실은 위 그림처럼, 혹은 더 복잡한 형태로 gradient mismatch 영향을 받을 가능성이 높다.

이럴 때 gradient mismatch를 줄일 간단고도 효과적인 레이아웃 전략이 있을까?

Center-Symmetric Pattern

두 개의 매칭되어야 할 디바이스가 있을 때 gradient 영향을 최대한 고르게 받게 하기 위한 패턴으로, 설명이 있으나 이해하기 어려울 것 같아 아래 그림들을 참고하면 되겠다.

이해을 돕기 위해 덧색을 입혀 보았다.

자세히 보면 order가 반복되면서 결국 기본배치 2 모양으로 배치가 되는 것을 알 수 있다.

물론 위의 배치는 정말 특성을 예술적으로 맞춰야 하는 경우에 참고하라고 소개한 것이고 실제는 4개의 cross-quad 배치를 반복하여 레이아웃하는 것이 현실적일 것이다.

앞서 소개한 기본 개념을 익히고 이런 복잡한 규칙을 적용할 수도 있다는 것을 알고 있으면 충분 할 것 같다.

저항, MOSFET, capacitor, BJT등에 대한 자세한 배치는 각각의 디바이스로 나누어 포스팅 하도록 하겠다.

'IC레이아웃' 카테고리의 다른 글

| MOS Transistor Matching Layout (0) | 2024.06.15 |

|---|---|

| Planar CMOS process (0) | 2024.06.14 |

| 레이아웃을 위한 반도체 공정(process) 기본 개념 (1) | 2024.05.25 |

| Layout Matching - 개념 및 종류 (2) | 2024.05.17 |

| [아날로그 레이아웃]Planar CMOS와 FINFET layout 차이점 (6) | 2024.05.06 |