MOS Transistor 레이아웃을 할 때 고려해야 할 또 다른 중요한 요소는 STI effect이다.

정확하게는 Shallow Trench Isolation stress effect 라고 한다.

공정이 미세화 되면서 STI 이외에도 여러가지 stress effect가 (특히 FINFET 공정에서) 대두되고 있지만, 이 중 가장 기본적인 STI stress effect에 대해 이야기해 보자.

먼저, STI란 디바이스와 디바이스를 분리해 주기 위한 구조이다. 쉽게 말하자면 active 와 active를 분리해 주는 역할을 한다.

250nm 이전의 공정에서는 아래 그림과 같이 LOCOS(Local Oxidation of Silicon) 구조를 사용하였는데, 이 구조는 공정 진행 과정에서 edge쪽의 산화막 형성이 덜 되어서 두께가 얇아지는 일명 Bird's peak 라고 부르는 모양이 형성된다.

공정 미세화가 진행되면서 이 Bird's peak 현상으로 인해 active를 효과적으로 분리시키는 데 한계에 이르렀기 때문에 LOCOS 대체용으로 적용된 것이 STI 구조이다.

STI 구조는 silicon에 에칭으로 좁고 깊은 틈을 만들고 그 틈에 Oxide를 채워 넣는 방식으로, 미세 공정에 적합하게 active 사이의 거리를 효과적으로 줄일 수 있게 되었다.

그러나 이렇게 개선된 STI 구조는 하나의 부작용이 있는데, 바로 오늘 다루고자 하는 STI stress effect이다.

좁고 깊게 형성된 Oxide와 Silicon은 재질이 다르기 때문에 서로 열팽창 계수도 다르다.

때문에 STI 구조와 active가 만나는 edge 쪽에서 응력이 작용하게 되는데, 이런 현상을 보통 stress라고 부른다.

아래 그림은 레이아웃 된 하나의 transistor에 이렇게 작용하는 stress의 크기를 보여 주는데, active edge에서 큰 stress가 작용함을 알 수 있다.

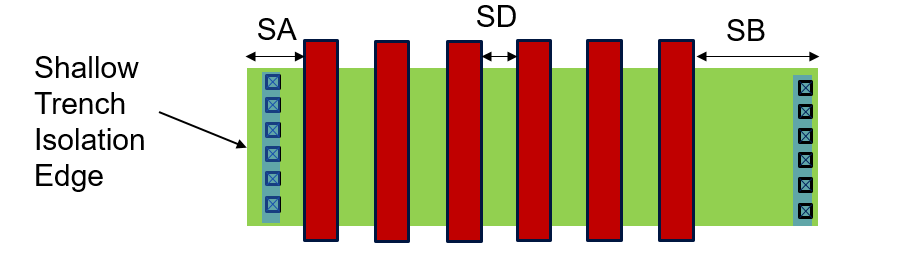

이렇게 작용하는 stress는 active adge쪽에 있는 MOS transistor의 Vth를 변화시키고, 결국 Id 전류도 변화시키는데, 만약 transistor가 하나의 active에 여러 개가 연결되어 있다면 active edge 쪽에 있는 transistor가 이 stress를 더 많이 받게 된다.아래 그림을 보면, 하나, 둘, 네 개의 transistor가 하나의 active에 형성되어 있을 때 gate의 위치에 따라 받는 STI stress 변화를 알 수 있다.

위의 그림은 마지막 빨간 네 개의 transistor와 같이 양 쪽에 더미 transistor을 사용한다면 안쪽에 있는 A, B는 STI stress 영향을 줄일 수 있다는 것을 보여준다.

그래서, 결론은?"아날로그 회로에서 중요한 transistor들의 STI effect를 줄이기 위해서는 양 쪽에 dummy transistor을 사용하여 레이아웃 할 것" 이 되겠다.Dummy를 꼼꼼히 넣어 본 사람들은 알겠지만 회로에도 반영하여야 하고 이게 사실 보통 귀찮은 일이 아니다.

하지만 지금껏 경험에 의하면 빈공간을 놔두지 않고 dummy를 잘 채웠을 때는 나중에 칩이 나왔을 때 어떻게든 좋은 쪽으로 써먹을 일이 있었지 나빴던 적은 없었다.

특히 전류 매칭이 아주 중요한 부분이라면 한 번은 더 확인해 보는 습관을 들이도록 하자.

'IC레이아웃' 카테고리의 다른 글

| 저항 matching technique (3) | 2024.07.08 |

|---|---|

| IC 레이아웃 - 저항의 개념과 종류 (5) | 2024.06.26 |

| MOS Transistor matching - Well Proximity Effect (WPE) (1) | 2024.06.19 |

| MOS Transistor Matching Layout (0) | 2024.06.15 |

| Planar CMOS process (0) | 2024.06.14 |