반도체 설계 시에는 다이오드나 트랜지스터와 같은 능동소자 이외에도 저항, 캐패시터, 인덕터 등의 수동수자들도 실리콘, 메탈과 같은 레이어로 구현할 수 있는데, 이 중 반도체에서 사용되는 저항의 기본적인 개념 및 종류에 대해 알아보기로 한다.

먼저, 저항이란?

말 그대로 어떤 물체에 전류가 흐르지 못하도록 방해하는 성질이라는 뜻으로 단위는 옴(ohm)으로 기호는

로 표시한다.

저항은 전류의 흐름에 저항하는 의미이기 때문에 물체의 양 단에 같은 전압이 가해졌을 때 저항이 크면 전류가 흐르기 어렵고 , 저항이 작으면 전류가 흐르기 쉽다. (옴의 법칙)

저항은 물질마다 서로 다른 값을 갖는데, 이렇게 물질이 가지고 있는 고유한 저항값을 비저항이라 부른다.

특정 물체의 저항은 그 물체의 비저항에 비례하고 물체의 길이에 비례하며, 단면적이 작을수록 커진다.

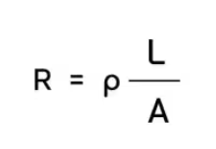

따라서 특정 물체에 대한 저항 R의 크기는 다음과 같은 수식으로 나타낼 수 있다.

그리고 위에서 설명한 특정 도체의 길이와 단면적, 저항과의 관계는 아래의 그림을 보면 이해하기 쉬울 것이다.

지금까지 설명한 것은 일반적인 도체에 대한 저항 개념이고, 반도체에서 사용되는 도체들은 두께가 일정한 매우 얇은 금속박막 형태로 사용되기 때문에 면저항(sheet resistance)으로 계산한다.

면저항은 Rs라는 기호로 나타내며 특정 레이어의 가로 세로 크기가 같을 때의 저항을 나타내는 값이다. 전체 저항값은 레이어의 길이에 비례하고 넓이에 반비례한다. 반도체 설계 업무를 할 때는 면저항이라는 표현보다는 sheet resistance라고 부른다.

위의 그림은 저항값을 면저항으로 표현하는 과정을 나타낸 것이다.

결론적으로 위에서 설명한 바와 같이 R=Rs(L/W) 가 된다.

이렇게 Rs 개념을 설명하는 이유는, 실제 반도체 설계시에는 Rs 값을 기준으로 저항을 계산하기 때문이다.

파운드리에서 디자인 룰이나 Eletric SPEC을 제공할 때에는 각 레이어에 대한 저항 정보는 모두 Rs 저항으로 정보가 제공이 된다. 따라서 레이아웃 전 후에 저항값을 계산할 때에는 각 레이어의 Rs 값과 실제 레이어의 width, length으로 전체 저항값을 계산해야 하니 위의 간단한 식은 외우고 있어야겠다.

그렇다면 반도체에서 저항은 어떤 종류가 있으며 실제로 어떻게 구현하는지 살펴보기로 하자.

반도체를 형성하는 물질 중에 저항 성분이 있는 모든 재료로 저항을 만들 수 있는데, 일반적인 CMOS 공정에서는 주로 well, active, poly, metal 의 네 가지로 저항을 만들 수 있다.

- WELL 저항

먼저, well 저항은 N-well로 만드는 것이 일반적이다.

P-well로도 만들수야 있겠지만 대부분의 CMOS 공정은 P-sub에 N-well 공정을 채택하고 있기 때문에 ground와 short되어 버리는 p-well 저항은 사용이 불가능하다.

그래서 물리적으로나 전기적으로 power, ground와 분리가 가능한 N-well로 저항을 만드는 것이 일반적이다.

N-well 저항의 layout 모양과 vertical 구조는 아래 그림과 같다.

N-well은 도핑농도가 낮기 때문에 큰 값의 저항을 구현하는 데 효과적이다.

CMOS 공정에서는 pmos의 body인 N-well을 power net으로 잡아주기 때문에 저항으로 사용되는 N-well은 short 방지를 위하여 저항이 아닌 N-well과는 분리를 해 주어야 한다.

위의 그림에서 표시한 바와 같이 N-well 저항의 width, length는 N-well에 연결된 active edge를 기준으로 측정하고, 이 값을 기본으로 저항값이 계산된다.

2. active 저항

두번째로 저항으로 사용될 수 있는 것은 active 이다. Active 레이어는 공정에 따라 diffusion 또는 ion-implant 공정으로 형성될 수 있기 때문에 어느 공정이 적용되느냐에 따라 기본 Rs 값이 차이가 있다.

N-active, P-active 모두 저항으로 사용 가능한데, diffusion, ion-implant 공정 차이 외에도 silicide 공정이 적용되냐 아니냐에 따라 레이아웃의 모양이 조금 달라진다.

먼저, silicide 공정을 적용하지 않는 라이브러리인 경우에는, 아래 그림과 같이 바로 메탈에서 active에 연결되는 contact 레이어를 기준으로 저항 length가 계산이 된다.

하지만 최근 공정은 대부분 active에 silicide 처리를 하고 있으므로, 이럴 때에는 SBL 이라는 레이어를 기준으로 저항의 length가 결정된다.

Silicide는 active나 poly의 저항을 줄여주기 위해 metalization 처리를 하는 공정이기 때문에 active와 poly 레이어의 저항이 없어져 버리는 결과가 된다. 따라서 저항으로 해당 레이어를 사용하기 위해서는 silicide 가 적용되지 않도록 blockage 레이어를 쳐줘야 하는데 이를 SBL(silicide blocking layer) 라고 부른다.

아래 그림은 이렇게 SBL 레이어를 추가하였을 때의 레이아웃 모양이다.

3. POLY 저항

세번째로 사용될 수 있는 레이어는 poly이다.

Active와 마찬가지로 해당 공정이 silicide를 적용하냐 아니냐에 따라 레이아웃 형태와 저항값 계산하는 length 기준이 달라지게 된다.

아래 그림을 참고하자.

4. METAL 저항

마지막으로 metal도 저항으로 사용할 수 있는데, 이 때에는 실제 저항 성분이 필요해서 사용하는 것은 아니고, simulation 수행이나 LVS 등의 필요에 의해 같은 메탈이지만 양 쪽의 net 이름을 분리해서 다른 이름으로 사용하고자 할 때 그 사이를 (회로적으로 short를 방지하기 위한) 저항으로 인식하기 위해 메탈 저항을 사용한다.

이 때 그려주는 저항 레이어는 mask로 만들어지는 레이어가 아닌 LVS 검증만을 위한 dummy 레이어이다.

이렇게 크게 4가지의 레이어를 이용하여 저항을 만들 수 있는데, Metal을 제외한 각각의 저항들은 아래 표와 같이 서로 다른 특성을 가진다. (정확한 특성은 각 공정마다 다르므로 파운드리에서 제공하는 ET spec으로 확인하여야 하며, 아래 표는 대체적인 경향을 나타낸다.)

| Nwell 저항 | active 저항 | poly저항 | ||

| diffusion | ion-implant | |||

| Rs | 1K~5K ohm/sq | 10~100 ohm/sq | 500~2K ohm/sq | 1K~5K ohm/sq |

| Absolute accurary | +/- 40% | +/- 35% | +/- 15% | +/- 3% |

| Relative accuracy | 5% | 2%(5u),0.2%(50u) | 2%(5u),0.15%(50u) | 2% |

| Tc | 4000ppm/C | +1500ppm/C | +400ppm/C | 500_1000ppm/C |

| Vc | 8000ppm/V | 200ppm/V | 800ppm/V | 100ppm/V |

Tc = Temperature Coefficiency

Vc = Voltage Coefficiency

이 중 아날로그 회로 설계 시에는 이 외에도 레이아웃 사이즈, parasitic 영향 등을 모두 고려하여 대부분 poly 저항을 사용하고 있다.

아날로그 회로에서 저항의 매칭에 관한 것은 다음 포스팅에서 다루도록 하겠다.

'IC레이아웃' 카테고리의 다른 글

| Capacitor 종류와 구조 (2) | 2024.08.03 |

|---|---|

| 저항 matching technique (3) | 2024.07.08 |

| MOS Transistor Matching - STI stress (LOD) (1) | 2024.06.19 |

| MOS Transistor matching - Well Proximity Effect (WPE) (1) | 2024.06.19 |

| MOS Transistor Matching Layout (0) | 2024.06.15 |