아날로그 레이아웃을 위한 회로에는 순수 아날로그 회로만 존재하는 것이 아니라 상당부분의 디지털 로직들도 포함하고 있다.

Clock driver 같은 경우는 모두 디지털이라 생각하면 되고, PLL의 경우도 많은 부분이 디지털 회로로 구성된다.

ADC, DAC 등의 컨버터 회로도 당연히 디지털과 아날로그 신호들을 포함하고 있어야 할 것이다.

그 외 많은 interface 회로들, 여러 블럭 내부의 control 회로 등등 수시로 디지털 로직을 그려야 하는 일이 생긴다.

수 기가비트로 동작하는 타이밍이 아주 까다로운 일부 블럭을 제외하고는 디지털 블럭 레이아웃은 몇 가지 기본사항만 알고 있으면 초보들도 얼마든지 잘 그릴 수 있는 회로인데, 그 몇 가지 기본 사항들에 대해 먼저 포스팅하고자 한다.

디지털 로직 레이아웃을 할 때 어디에 중점을 둬야 하나요? 라고 묻는다면 무조건 크기가 작게 그리라고 답할 수 있다.

디지털 로직은 0과 1의 신호만 전달하기 때문에 쓸 데 없이 guardring을 공들여 그릴 필요도 없고, 대부분의 경우 guardring을 공들여 그린 것과 그렇지 않는 것과의 사이에 의미 있는 특성 차이도 없다.

간혹 (아날로그 레이아웃에 포함되어 있는 로직이니까) 순수 아날로그 회로와 같은 수준으로 MOS를 배치하고 guardring을 네모로 둘러치고 하는 엔지니어들이있는데, 그렇게 하면 레이아웃 사이즈만 커지고 작업하는 시간만 늘어나기 때문에 권하지 않는다. 그 시간에 다른 중요 블럭의 배치와 라우팅을 더 살펴보는 것이 특성에는 도움이 될 것이다.

다만, 디지털 로직이 I/O 영역에 가까이 있어서 latch-up rule의 적용해 주어야 하는 경우에는 예외로 guardring을 네모난 ring 형태로 둘러 쳐 주어야 한다.

또한 대부분의 아날로그 회로 control 로직은 0또는 1의 DC 신호로 고정이 되는 회로가 많다. 이런 회로들은 라우팅이 아무리 지저분해 보여도 서로의 신호간에 영향을 줄 일이 전혀 없으니 아날로그 블럭들을 배치하고 남은 공간에 잘 끼워놓기만 해도 된다.

디지털 로직이 포함되어 있는 회로를 보고 잘 모를 때에는 회로 설계자에게 고속 동작하는 부분이 있는지, clock 에 해당되는 path가 어디인지 정도만 확인하고 그 부분만 잘 신경쓰면 될 것 같다.

그럼, 실제 레이아웃 패턴의 예를 들어 설명해 보기로 한다.

1) Metal(VIA 포함), active 를 제외한 다른 레이어는 merge 한다.

Nand, nor 등의 레이아웃을 위해 회로에 있는 디바이스 그대로 PDK를 가져다 놓으면 아래와 같이 p-implant, n-implant, n-well 등의 모든 레이어를 포함된 PDK로 뿌려지는데, 왕초보들은 이 때 n-well, p-implant, n-implant 레이어들도 모두 분리하여 레이아웃 하기도 한다. (인터넷 검색 시 흔히 나오는 유형)

Level-shifter로 분리되지 않는 이상 로직의 Nwell bias는 VDD로 잡히게 되어 있으므로 n-well, p-implant, n-implant 레이어들은 모두 merge 해 주어야 size를 줄일 수 있다.

레이아웃 시 분리해 주어야 하는 레이어는 short 되면 안되는 metal, poly, active 및 서로 다른 bias를 가진 n-well 이다.

2) 동일한 블럭이나 IP에서 함께 사용되는 로직은 cell height 를 동일하게 맞춰준다.

이렇게 모든 cell들의 키높이를 맞춰 주어야 복잡한 로직회로에서 로직 cell들을 마구 섞어 배치를 해도 DRC 에러 없이 빠르고 안전하게 레이아웃을 할 수 있다.

이 때 단위 Tr의 width가 너무 커서 전체 로직 면적이 지나치게 커진다 싶으면 회로 설계자에게 문의하여 적당한 width의 multi-finger로 쪼개어 준다. 대부분의 로직에서는 total width가 같으면 문제되지 않는다.

3) Guardring의 위치는 power, ground line 아래로 잡도록 하며, 로직 cell의 좌우로 guardring을 넣지는 않는다(공간낭비).

Guardring 위치, Nwell, P-implant 영역, N-implant 영역의 Y축 위치는 동일하게 하면 로직 cell들을 딱 붙였을 때 drc error를 방지할 수 있다.

이렇게 Y축 위치를 딱 잡아 놓고 전체 로직 cell 레이아웃을 진행하다가 PMOS 또는 NMOS 사이즈가 튀는 cell이 있어서 곤란할 때가 있는데, 이 때는 좌우에 다른 cell과 만나는 부분만 기준에 맞도록 레이아웃을 하면 된다.

이것도 불가능할 때에는 그냥 DRC error가 발생하지 않을 정도로 다른 cell들로부터 분리하여 그린다.

4) Latch-up rule로 인하여 네모난 형태의 guardring을 적용하여야 하는 경우에는 모든 cell 내부에 네모난 guardring을 넣는 것이 아닌, 전체 로직 배치 후 하나의 네모난 guardring을 그려주어야 레이아웃이 지나치게 커지지 않는다.

그리고 이런 로직은 PMOS 와 NMOS 사이에 guard ring이 추가되어야 하므로 그만큼의 공간을 생각하고 위아래로 여유있게 디바이스를 배치해야 한다는 점도 잊지 말아야겠다.

5) Contact 및 via는 2개 이상 적용한다. 단, 작은 device를 사용하거나 FINFET 공정 적용으로 인하여 어쩔 수 없는 경우는 제외.

6) 위아래 guardring의 contact pitch의 N배수로 로직 셀의 가로 크기를 결정한다.

이 때 contact space는 minimum rule에 따를 필요는 없고 로직들의 가로 사이즈를 고려하였을 때 적당한 space를 찾아서 정하면 된다.

아래 예제에서는 contact을 한 줄로 사용하였는데, 두 줄 혹은 세 줄로 레이아웃 하여도 무방하다.

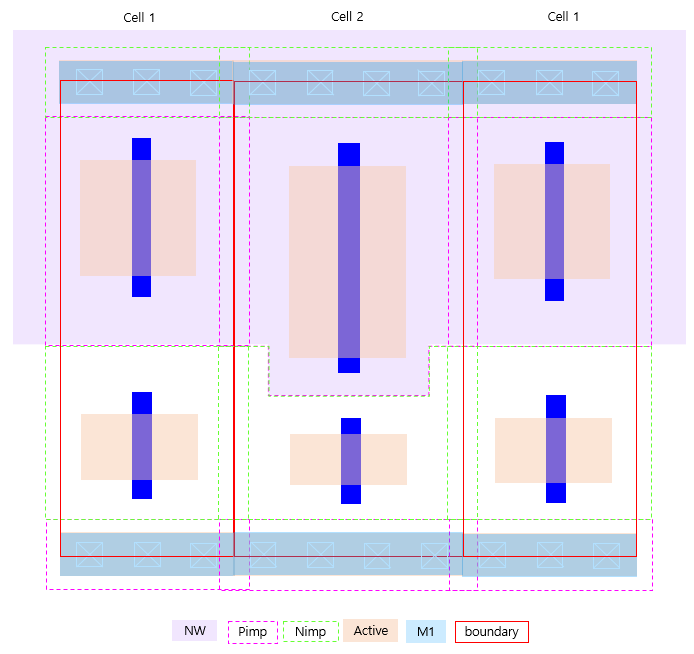

7) 로직 cell을 세로로 쌓아서 배치 할 때에는 P-N-N-P 와 같이 한 쪽은 위아래로 뒤집어서 배치하여 contact layer를 공유하도록 하면 전체 크기를 줄일 수 있는데, 흔히 볼 수 있는 로직 레이아웃 예를 보자.

아래 그림과 같이 배치를 하면 몇 가지 단점이 발생하는데, 먼저 윗부분부터 디바이스 배치가 P-N-P-N 순서로 반복되기 때문에 parasitic diode 성분이 많아지게 된다. 기본적으로 반도체 레이아웃에서는 P,N junction을 최소화 하도록 레이아웃 해야 하므로 이런 패턴은 권장하지 않는다.

또한 power 공급 라인이 VDD-VSS-VDD-VSS 로 로직 한 줄 당 VDD,VSS를 모두 공급해 주어야 하므로 라우팅 공간이 더 필요하게 되었고, 위 아래 로직들을 모두 분리하여야 하므로 레이아웃 배치 공간 또한 넓어지게 되었다.

이러한 단점들을 보완하기 위해 6번 항목과 같이 guardring의 contact 을 꼼꼼하게 맞춰 주었는데, 모든 로직 cell의 guardring 위치와 contact 위치를 잘 맞춰 주었다면 아래와 같이 배치를 하면 된다.

자세히 보면 알겠지만 위, 아래 로직들의 guard-ring을 공유하도록 배치한다.

윗줄이나 아랫줄의 로직 cell들을 위아래로 flip하여 contact 센터를 기준으로 맞추면 된다.

이렇게 하면 위, 아래 줄의 power나 ground 라인을 공유할 수 있기 때문에 레이아웃 사이즈도 작아지고 power 라우팅 공간도 훨씬 절약 할 수 있다. 또한 디바이스 배치도 P-N-N-P 순서가 반복되도록 배치 할 수 있기 때문에 P,N junction 도 훨씬 줄어들 수 있다.

8) filler 사용

로직을 배치하다 보면 라우팅의 편리성이나 제각각인로직 cell 가로 사이즈, 또는 다른 여러가지 이유로 인하여 아래 그림과 같이 중간 중간 빈 공간이 생기기도 한다.

이렇게 비어 있는 상태로 그냥 두면 잘못하다가 좌, 우의 power line이 연결되지 않거나 하는 문제가 발생할 수 있다. 그래서 이런 공간은 filler라는 cell을 사용하여 n-well. guardring 등을 채워주면 편리하다.

보통은 guardring의 contact 하나가 들어가는 사이즈(1 contact pitch)의 cell로 만들어 놓고 빈 공간에 mosaic 개수를 조절하여 채워 놓는데, 필자는 contact 개수만 입력하면 되도록 p-cell로 만들어서 사용하는 편이다.

자, 오늘은 로직 레이아웃 준비 편으로 본격적인 로직 레이아웃 전에 알아 두어야 할 몇 가지를 설명하였다.

물론 이 내용들은 필수적인 것은 아니지만 대체적으로 이렇게 레이아웃 한다는 정도로 이해하면 될 것 같다.

다음에는 인버터부터 초보자들이 실제 따라그리면 되는 로직 레이아웃을 포스팅 할 예정인데, 새로 그려야 하는 그림이 많아서 어느 정도 속도로 올릴 수 있을지는 모르겠다.......

'Logic 레이아웃' 카테고리의 다른 글

| 그대로 따라 그리는 로직 레이아웃 - edge triggered D flip-flop (4) | 2025.01.10 |

|---|---|

| 그대로 따라 그리는 로직 레이아웃 - transmission gate (또는 switch) (2) | 2024.11.24 |

| 그대로 따라 그리는 로직 레이아웃 - schmitt trigger buffer (1) | 2024.11.18 |

| 그대로 따라 그리는 로직 레이아웃 - buffer,nand,nor (0) | 2024.11.12 |

| 그대로 따라 그리는 로직 레이아웃- 레이아웃의 시작, 인버터 (7) | 2024.10.17 |